论文随记

论文随记

论文随记

问题

- craterlake如何做host与device的通信? 这与hpu并不相同(不存在加速卡的通信问题?),是否偏离主线的问题。

- 并行需要

上次提到的点

- 如何提高加速器的并行性,即提高同一时间计算单元使用率

- 如何排布数据在存储器中来减少数据冲突,因为并行计算的时候可能会有多个计算单元访问同一数据

- 与host端通信的问题

下一步工作

指令集并行的优化空间不大,考虑多面体模型的应用 创建统一的硬件接口,参考tpu-mlir,fhe加速器综述,GPU的类似工作

需要考虑

- 存储结构

- craterlake的存储结构是,2048通道,且共用一个256MB的寄存器

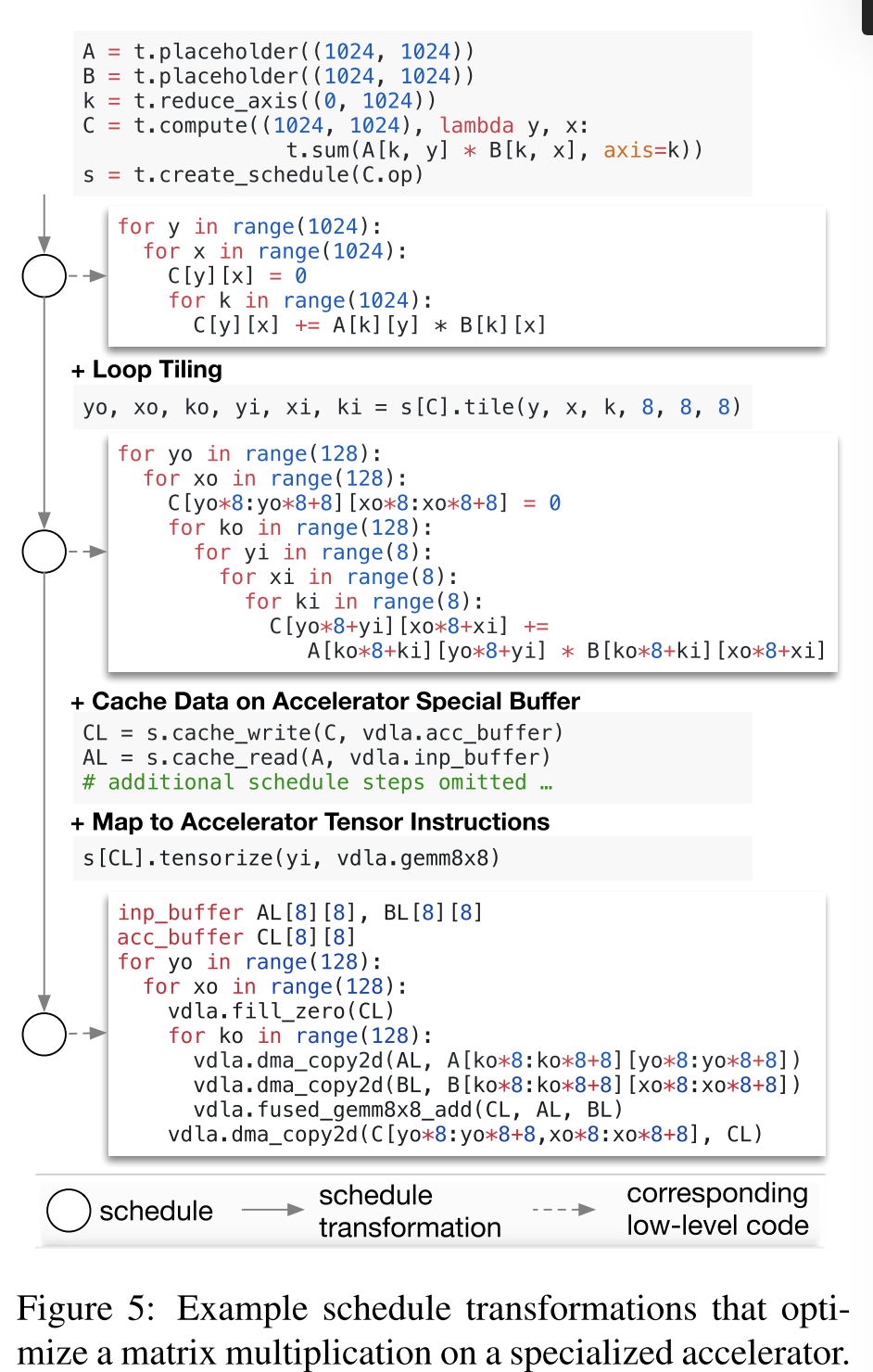

- 加速器与其他硬件的区别,针对这一区别在编译器中做了什么优化,参考ai编译器

- 计算单元数量庞大,且计算单元功能单一

- 存储结构与传统cpu/gpu不同

- 内存访问延迟:CPU与GPU会通过乱序执行或海量线程掩盖计算远快于内存访问延迟的问题,专用加速器将这一点交给了编译器处理。

- 算子融合优化:参考TVM的算子融合,需要验证在craterlake上是否适用以及heir等编译器是否已经有算子融合优化。

- 流水线优化:调度指令隐藏流水线停顿

- 数据布局优化:不同于密文内部的数据布局(如fhelipe等),此乃针对内存的数据布局

- 哪些layer放到加速器上,哪些在cpu上跑

- 针对硬件的优化可能存在较大的搜索空间,可以引入智能体对其进行搜索

参考

- google heir

- tpu-mlir

本文由作者按照 CC BY 4.0 进行授权